طراحی سیستم با استفاده از Verilog

✅ سرفصل و جزئیات آموزش

آنچه یاد خواهید گرفت:

- کدنویسی Verilog برای مدارهای دیجیتال

پیش نیازهای دوره

- هیچ الزامی وجود ندارد.

توضیحات دوره

پس از اتمام این دوره، فراگیران قادر خواهند بود:

(1) مفاهیم معیارهای طراحی که باید توسط مهندس طراحی بهینه شوند را درک کنند.

(2) مفاهیم فناوری طراحی IC را بفهمند.

(3) اجرای منطق با استفاده از فناوری آی سی با عملکرد ثابت، فناوری ASIC کاملاً سفارشی و فناوری ASIC نیمه سفارشی را درک کنند.

(4) مزایا و معایب استفاده از فناوری آی سی با عملکرد ثابت، فناوری ASIC کاملاً سفارشی و فناوری ASIC نیمه سفارشی برای پیادهسازی منطق را بشناسند.

(5) مفهوم پیادهسازی منطق در PLDها را بفهمند.

(6) مفهوم پیادهسازی منطق در FPGA را درک کنند.

(7) جریان طراحی IC را بشناسند.

(8) نقش HDL در طراحی سیستم را درک کنند.

(9) مفاهیم ساختارهای مختلف زبان Verilog را بفهمند.

(10) انواع عملگرها و کاربردهای آنها در کدنویسی Verilog را بشناسند.

(11) نحوه استفاده از نرمافزار Xilinx برای نوشتن کد Verilog را یاد بگیرند.

(12) نحوه استفاده از نرمافزار Xilinx برای شبیهسازی کد Verilog را یاد بگیرند.

(13) نحوه استفاده از نرمافزار Xilinx برای پیادهسازی کد Verilog را یاد بگیرند.

(14) منطق ترکیبی را با استفاده از سبک مدلسازی رفتاری پیادهسازی کنند.

(15) منطق ترکیبی را با استفاده از سبک مدلسازی جریان داده پیادهسازی کنند.

(16) منطق ترکیبی را با استفاده از سبک مدلسازی ساختاری پیادهسازی کنند.

(17) منطق ترتیبی را با استفاده از سبک مدلسازی رفتاری پیادهسازی کنند.

(18) منطق ترتیبی را با استفاده از سبک مدلسازی جریان داده پیادهسازی کنند.

(19) منطق ترتیبی را با استفاده از سبک مدلسازی ساختاری پیادهسازی کنند.

(20) منطق را با استفاده از ترانزیستورهای mos پیادهسازی کنند.

این دوره برای چه کسانی مناسب است؟

- دانشجویانی که علاقهمند به نوشتن و شبیهسازی کدهای Verilog برای مدارهای ترکیبی و ترتیبی هستند.

طراحی سیستم با استفاده از Verilog

-

معیارهای طراحی 14:56

-

فناوری Fixed Function IC (آی سی با عملکرد ثابت) 24:46

-

فناوری ASIC کاملاً سفارشی 31:58

-

فناوری ASIC نیمه سفارشی 25:24

-

نقش HDL در طراحی سیستم 51:37

-

فناوری PLD (PLA) 30:52

-

فناوری PLD (PAL) 17:20

-

FPGA (معماری) 37:54

-

FPGA (نمونههای پیادهسازی منطق) 29:01

-

چالش خود را بسنجید - 1 None

-

معرفی زبان Verilog 23:25

-

سطح انتزاع 20:41

-

معرفی نرمافزار Xilinx 15:04

-

انواع داده (انواع شبکه) 24:40

-

انواع داده (انواع رجیستر) 34:09

-

عملگر (عملگرهای بیت به بیت) 28:21

-

عملگر (منطقی و کاهش) 32:21

-

عملگر (حسابی، رابطهای و شیفت) 29:11

-

عملگر (الحاق، شرطی و تکرار) 27:23

-

چالش خود را بسنجید – 2 None

-

معرفی مدلسازی در سطح ساختار 46:54

-

معرفی مدلسازی در سطح رفتاری 41:39

-

معرفی مدلسازی در سطح جریان داده 35:52

-

تست بنچ - (قسمت 1) 48:38

-

تست بنچ - (قسمت 2) 35:15

-

تست بنچ - (قسمت 3) 27:39

-

مدلسازی ساختاری (مالتیپلکسر 2 به 1) 31:41

-

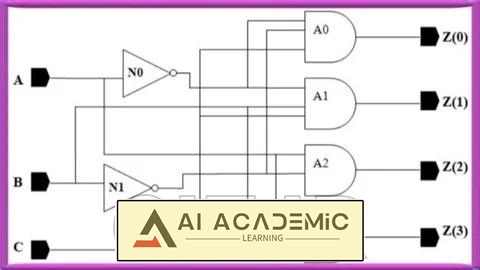

مدلسازی ساختاری (کدگذار 2 به 4) 23:40

-

مدلسازی ساختاری (جمعکننده 3 بیتی) قسمت 1 29:32

-

مدلسازی ساختاری (جمعکننده 3 بیتی) قسمت 2 19:56

-

دستورات رویه ای 45:22

-

دستورات ترتیبی (if-else) قسمت 1 33:50

-

دستورات ترتیبی (if-else) قسمت 2 22:55

-

دستورات ترتیبی (if-else) قسمت 3 33:21

-

دیکودر 2 به 4 با استفاده از دستور if-else 18:13

-

مقایسهکننده با استفاده از دستور “if-else” 26:16

-

نمایش نرمافزاری مقایسهکننده 09:42

-

مالتیپلکسر 2 به 1 با استفاده از دستور “case” 13:38

-

مالتیپلکسر 4 به 1 با استفاده از دستور “case” 15:10

-

دیکودر 2 به 4 با استفاده از دستور “case” 16:31

-

مقایسهکننده 1 بیتی با استفاده از دستور “case” 18:02

-

دیکودر BCD به 7 سگمنت با استفاده از دستور “case” 26:05

-

دستورات ترتیبی - (حلقه) 35:22

-

کد Verilog فلیپفلاپ D 46:28

-

کد Verilog فلیپفلاپ JK 44:09

-

کد Verilog فلیپفلاپ T 23:37

-

کد Verilog شمارنده 3 بیتی 27:46

-

رجیستر ورودی موازی و خروجی موازی 29:50

-

رجیستر ورودی سریالی و خروجی موازی 25:10

-

رجیستر ورودی سریالی و خروجی سریالی 29:19

-

چندین بلوک always - (مثال) 26:18

-

چندین بلوک always - (فلیپفلاپ D) 18:40

-

چندین بلوک always - (دیکودر 2 به 4) 33:22

-

دستور Blocking 27:15

-

دستور Non-Blocking 30:30

-

مدل Verilog جمعکننده کامل 28:16

-

مبدل باینری به گری 31:48

-

مبدل گری به باینری 37:13

-

کد Verilog دیمالتیپلکسر 1 به 2 13:52

-

انکودر اولویت 29:57

-

سوئیچ “cmos” (قسمت 1) 42:33

-

سوئیچ “cmos” (قسمت 2) 17:44

-

سوئیچ “cmos” (قسمت 3) 15:16

-

سوئیچ “cmos” (قسمت 4) 11:55

-

UDP (قسمت 1) 18:34

-

UDP (قسمت 2) 29:56

-

UDP (قسمت 3) 15:23

-

UDP (قسمت 4) 16:14

مشخصات آموزش

طراحی سیستم با استفاده از Verilog

- تاریخ به روز رسانی: 1404/06/21

- سطح دوره:متوسط

- تعداد درس:68

- مدت زمان :30:25:21

- حجم :18.01GB

- زبان:دوبله زبان فارسی

- دوره آموزشی:AI Academy