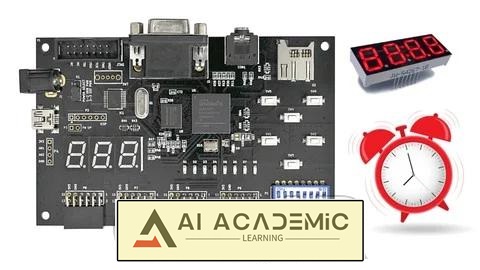

یادگیری عملی طراحی FPGA: ساخت ساعت زنگدار

✅ سرفصل و جزئیات آموزش

آنچه یاد خواهید گرفت:

- تحلیل مشخصات: درک نیازمندیهای سیستم و مشخصات طراحی برای یک پروژه مبتنی بر FPGA

- طراحی منطق دیجیتال با VHDL: طراحی مدارهای منطقی ترکیبی و ترتیبی

- مبانی FPGA: کسب تجربه عملی با سختافزار FPGA، زنجیرههای ابزار و گردش های کاری توسعه

- دستگاه بازر: یادگیری چگونگی ارتباطدهی و راهاندازی یک بازر برای تولید صدای زنگ

- نمایشگر 7-Segment: یادگیری چگونگی ارتباطدهی و راهاندازی یک نمایشگر 7-segment خارجی برای نمایش زمان

- ارتباطدهی دکمه فشاری و سوئیچ: درک چگونگی اتصال و حذف نویز دستگاههای ورودی مانند دکمهها و سوئیچها

- سنتز و شبیهسازی FPGA: استفاده از ابزارهای شبیهسازی برای تأیید طرح قبل از سنتز آن روی سختافزار

- نمایش سیستم نهایی: ارائه یک سیستم ساعت زنگدار فعال که روی بورد FPGA اجرا میشود.

پیشنیازهای دوره

- برای بهرهبرداری کامل از این دوره، آشنایی با مفاهیم اولیه الکترونیک دیجیتال و VHDL مورد نیاز است.

توضیحات دوره

این دوره طراحی شده است تا شما را در دنیای مهندسی سختافزار غرق کند. این دوره شما را در فرآیند تبدیل نیازمندیها و نیازها به طرحهای عملی و کارآمد راهنمایی میکند. شما مفاهیم پایه مدارهای دیجیتال و قواعد کدنویسی و سینتکس VHDL را بررسی خواهید کرد. علاوه بر این، دوره شامل استفاده از فایلهای محدودیت، سنتز و شبیهسازی طرحهای HDL میشود که به شما امکان میدهد قبل از پیادهسازی فیزیکی، صحت مدارهای خود را تأیید کنید. در پایان دوره، شما مجموعه مهارتهای جامعی برای طراحی، پیادهسازی و تست سیستمهای دیجیتال خواهید داشت.

برای دستیابی به تمام موارد فوق، مدرس یک ساعت زنگدار را با VHDL روی FPGA طراحی خواهد کرد. یک نمایشگر 7-segments چهار رقمی خارجی از طریق سیم به FPGA متصل خواهد شد تا زمان را با فرمت HH:MM نمایش دهد. این کار برای یادگیری درباره PMODهای FPGA و پینهای ورودی/خروجی ایدهآل است. این طرح به کاربر اجازه میدهد تا با استفاده از سوئیچها، زمان فعلی یا ساعت زنگدار را تنظیم کند. در حالت "SET"، پیکربندی ساعت و زنگ با فشار دادن دکمههای فشاری برای افزایش دقیقهها یا ساعتها انجام میشود. زمانی که زمان فعلی به زمان زنگ تنظیم شده توسط کاربر برسد، یک بازر متصل به FPGA برای یک دقیقه بوق میزند.

در پایان دوره، دانشجویان مهارتهای عملی و تجربه لازم برای طراحی، پیادهسازی و تأیید سیستم ساعت زنگدار دیجیتال کاملاً کاربردی خود روی FPGA را خواهند داشت که اصول محکم برای پروژههای بعدی طراحی FPGA و دیجیتال فراهم میکند.

این دوره برای چه کسانی مناسب است؟

- دانشجویان مبتدی الکترونیک دیجیتال یا هر کسی که علاقهمند به یادگیری طراحی FPGA است.

یادگیری عملی طراحی FPGA: ساخت ساعت زنگدار

-

مقدمه 01:38

-

مشخصات 07:24

-

تجهیزات استفاده شده 04:33

-

بورد FPGA مدل Mimas V2 03:36

-

بازر 04:07

-

نمایشگر 7-segment چهار رقمی 12:12

-

بردبورد 04:45

-

پورتهای ورودی/خروجی 02:38

-

حذف نویز دکمه 06:01

-

تقسیمکننده کلاک 11:01

-

شمارندهها 12:03

-

تبدیل باینری به BCD 11:45

-

کنترلر بازر 08:27

-

کنترلر نمایشگر 08:45

-

ساعت زنگدار 03:12

-

شبیهسازی 15:01

-

سنتز 01:28

-

نمایش عملکرد 04:06

-

سخن پایانی 00:45

مشخصات آموزش

یادگیری عملی طراحی FPGA: ساخت ساعت زنگدار

- تاریخ به روز رسانی: 1404/10/04

- سطح دوره:همه سطوح

- تعداد درس:19

- مدت زمان :02:03:27

- حجم :951.0MB

- زبان:دوبله زبان فارسی

- دوره آموزشی:AI Academy